Professor Tetsuo Endoh's Group at Tohoku University's Center for Innovative Integrated Electronics has announced a new magnetic tunnel junction (MTJ) quad-technology that provides better endurance and reliable data retention - over 10 years - beyond the 1X nm generation.

This novel Quad technology meets the design requirements for the state-of-the-art X nm complementary metal-oxide semiconductor (CMOS) node and will pave the way for ultra-low-power consumption for Internet of Things (IoT) edge-devices in mobile communication, the automotive industry, consumer electronics, and industrial/infrastructure equipment.

The results will be presented in June at an international conference on semiconductor ultra-large scale integrated circuits entitled "2021 Symposia on VLSI Technology and Circuits." The conference takes place from June 13 to 19.

Developing smart societies through the use of the IoT, AI, and networks based on the next-generation mobile communication systems requires edge devices to be more power-efficient. A greater power efficiency also aids the goal of becoming carbon neutral.

Many logic circuits embedded with spin transfer-torque magnetoresistive random access memory (STT-MRAM) as a low power consumption technology. However, meeting the design rules of the X nm CMOS requires the MTJ diameter to be formed using the back end of line (BEOL) process and must fabricate at 1X nm generation.

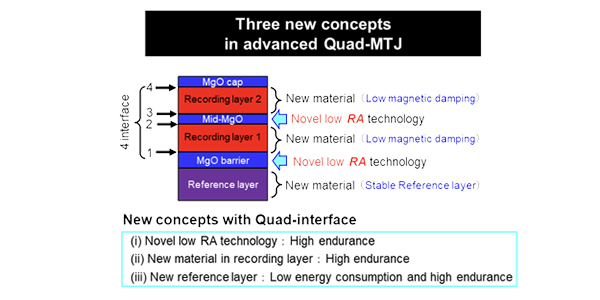

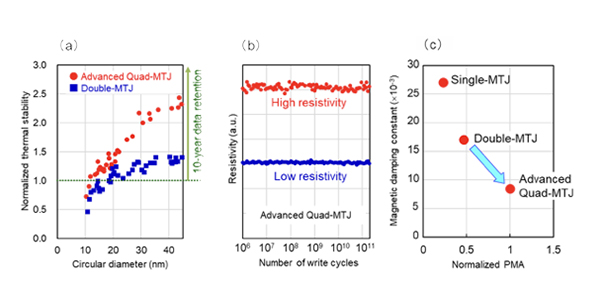

The developed Quad-interface MTJ (Quad MTJ) - the first of its kind - has three new technologies: (i) a low RA technology, (ii) a low damping material in the recording layer, and (iii) a stable reference layer.

This enabled it to have (1) better retention characteristics of over 10 years, (2) endurance that exceeded at least 6 X 1011, (3) a high-speed write operation of 10 nanoseconds, (4) a low power consumption operation of 20%, and (5) a low write error rate combined with a circular diameter of 18 nm. Additionally, the Quad-MTJ has high retention and high endurance characteristics at a 10 ns high-speed operation. This is the first time in the world that severe conditions 1 - 5 have been realized at the 1X nm generation.

The 18nm Quad-MTJ possesses a large capacity STT-MRAM technology that is smaller than static random access memory (SRAM). As such, it is expected to replace SRAM for the X nm generation in CMOS logic. This means that STT-MRAM's application can expand to the leading-edge logic, achieving ultra-power consumption, excellent scalability and high reliability in application processors.

- Publication Details:

Title: Advanced 18 nm Quad-MTJ technology overcomes dilemma of Retention and Endurance under Scaling beyond 2X nm

Authors: H. Naganuma, S. Miura, H. Honjo, K. Nishioka, T. Watanabe, T. Nasuno, H. Inoue, T. V. A. Nguyen, Y. Endo, Y. Noguchi, M. Yasuhira, S. Ikeda, and T. Endoh

Conference: 2021 Symposia on VLSI Technology and Circuits

雷速体育_中国足彩网¥在线直播:

Tetsuo Endoh

Center for Innovative Integrated Electronic Systems, Tohoku University

Email: tetsuo.endoh cies.tohoku.ac.jp

cies.tohoku.ac.jp

Website: http://www.cies.tohoku.ac.jp/english/